RISC-V alla riscossa: la prima CPU per server, processori fino a 512 core e microcontrollori

di Riccardo Robecchi pubblicata il 16 Dicembre 2022, alle 17:21 nel canale Device

Il RISC-V Summit ha visto la presentazione di molte novità parecchio interessanti, dalle prime CPU per server (prodotte da Ventana), fino a processori con un massimo di 512 core (a marchio MIPS!) e microcontrollori (da XMOS)

L'architettura RISC-V sta vivendo un momento di particolare interesse da parte delle aziende, che sembrano sempre più interessate a essa e continuano a sviluppare nuove soluzioni. Al RISC-V Summit che si sta tenendo questa settimana a San Jose, in California, sono state presentate diverse novità, tra cui i primi processori RISC-V per server a opera di Ventana, il primo core RISC-V a marchio MIPS e l'adozione dell'architettura da parte di XMOS, noto produttore britannico di microcontrollori.

RISC-V sbarca nel mercato server grazie a Ventana

Ventana ha annunciato il primo processore RISC-V per server, chiamato Veyron V1. Sebbene non siano stati diffusi dati sulle prestazioni della nuova CPU, l'azienda ha comunicato diversi dettagli sull'implementazione dell'architettura. Il chip userà infatti una pipeline a otto stadi con un motore "aggressivamente" out of order (ovvero in grado di eseguire le istruzioni fuori dall'ordine con cui sono scritte, fatto che incrementa spesso le prestazioni), con una frequenza massima di 3,6 GHz. Le CPU potranno avere fino a 128 core, divisi in gruppi di 16, e saranno disponibili fino a 48 MB di cache L3 per ciascun gruppo, equivalenti a 3 MB per ciascun core. I processori saranno realizzati da TSMC con un processo produttivo a 5 nm.

Ventana ha rimarcato come i processori integrino contromisure avanzate contro gli attacchi di tipo side channel, che hanno coinvolto (e, per molti versi, anche sconvolto) il mercato delle CPU negli scorsi anni, in particolare nel mondo x86. I Veyron V1 forniranno inoltre funzionalità avanzate per la virtualizzazione come IOMMU e AIA (Advanced Interrupt Architecture).

L'intenzione di Ventana è quella di creare dei processori eterogenei, con chiplet forniti da diverse realtà integrati nello stesso chip (chiplet si può tradurre letteralmente con "chippettino" ed è pensabile come un modulo di un chip). L'azienda ha sviluppato una tecnologia per connettere i vari chiplet che riduce sensibilmente la latenza e permette di ottenere prestazioni simili a quelle dei processori su die monolitico.

Il lancio dei primi processori Ventana Veyron V1 è previsto per il secondo o terzo trimestre del 2023.

MIPS lancia i primi core con architettura RISC-V

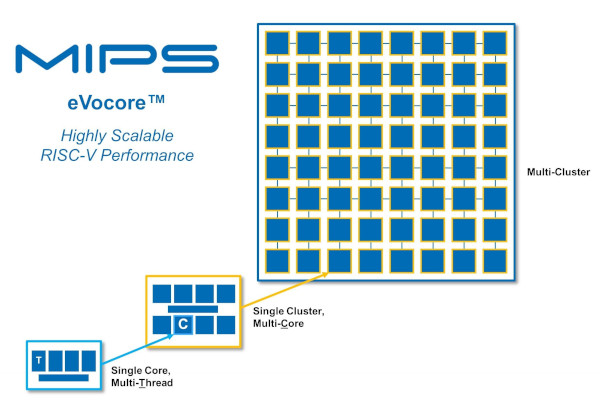

Il nome MIPS ha avuto fortune alterne e, dopo il periodo d'oro negli anni '80 e '90, ha visto un progressivo declino negli ultimi 15 anni. I processori MIPS erano usati anche in prodotti di larghissima diffusione, come la Sony PSP e il Nintendo Wii. Ciò non è bastato, però, a salvare l'azienda, che è stata acquisita da Imagination Technologies qualche anno prima del tracollo anche di quest'ultima. MIPS ora si dedica allo sviluppo di processori RISC-V e ha appena annunciato il suo primo prodotto: l'eVocore P8700, che l'azienda definisce come "il processore RISC-V più scalabile e con le maggiori prestazioni" sul mercato.

Il P8700 offre l'esecuzione out of order delle istruzioni assieme al multithreading. Il processore è composto di gruppi di 16 core, con un massimo di 64 cluster per un totale di 512 core e di 1.024 thread (che nel gergo di RISC-V sono chiamati "harts", da "hardware threads").

L'azienda afferma che può essere impiegato negli ambiti più vari, dalle automobili fino all'HPC. Gli eVocore P8700 sono già stati concessi in licenza a Mobileye per la realizzazione di soluzioni come ADAS e guida autonoma.

XMOS sceglie RISC-V per i propri microcontrollori

XMOS è un nome forse meno noto ai più, ma i suoi microcontrollori sono particolarmente apprezzati, ad esempio, nell'ambito dell'audio, dove vengono spesso usati per gestire le connessioni USB. Finora l'azienda ha usato un set di istruzioni proprietario, ma a partire dall'anno prossimo i suoi prodotti useranno invece l'ISA RISC-V.

Come riporta The Register, l'azienda ha di fatto apportato modifiche relativamente minori alla sua architettura per renderla compatibile con RISC-V, in particolare riguardo la grandezza dei registri. Il fatto che RISC-V sia nativamente estensibile ha reso possibile creare nuove istruzioni che permettessero di mantenere la compatibilità con le precedenti architetture di XMOS.

Ciascun chip potrà essere assemblato in moduli, ciascuno dei quali dotato di due core in grado di gestire fino a otto thread in hardware. Particolarità dei microcontroller XMOS è il fatto che funzioni normalmente implementate in hardware vengono, invece, delegate al software; per fare un esempio, la seconda serie di microcontroller xcore ha introdotto la possibilità di gestire connessioni Gigabit Ethernet con un adattatore implementato via software.

L'architettura RISC-V, dunque, sembra pronta a prendere d'assalto praticamente ogni ambito, dai microcontrollori fino al calcolo ad alte prestazioni. La sua flessibilità, apertura e mancanza di un controllo centralizzato, coniugata però a uno standard ben definito che è già stato sfruttato per creare software, sta diventando sempre più attraente per molte aziende. È interessante pensare come la crescita di ARM nel mondo server potrebbe portare anche a una crescita di RISC-V: l'esplorazione di architetture alternative apre a una maggiore flessibilità più in generale da parte delle aziende, con il risultato che anche RISC-V potrebbe avere la sua occasione.

AWS re:Invent 2025: inizia l'era dell'AI-as-a-Service con al centro gli agenti

AWS re:Invent 2025: inizia l'era dell'AI-as-a-Service con al centro gli agenti Cos'è la bolla dell'IA e perché se ne parla

Cos'è la bolla dell'IA e perché se ne parla BOOX Palma 2 Pro in prova: l'e-reader diventa a colori, e davvero tascabile

BOOX Palma 2 Pro in prova: l'e-reader diventa a colori, e davvero tascabile Dreame entra nel mercato smartphone: trapelano le specifiche del primo E1

Dreame entra nel mercato smartphone: trapelano le specifiche del primo E1 Cloudflare, nel 2025 un web a due facce: Internet più veloce ma anche meno libera

Cloudflare, nel 2025 un web a due facce: Internet più veloce ma anche meno libera Riot prepara 'League Next': il futuro di League of Legends passa dal 2027

Riot prepara 'League Next': il futuro di League of Legends passa dal 2027

4 Commenti

Gli autori dei commenti, e non la redazione, sono responsabili dei contenuti da loro inseriti - infoNintendo 64, PlayStation, Playstation 2, PSP, se si vogliono fare i nomi corretti.

Oltre che questa MIPS non centra niente con quella storica, nell'intertempo è fallita un numero di volte seconda solo a Commodore.

cavoli se ne è passato di tempo

https://it.wikipedia.org/wiki/IBM_System_p

https://it.wikipedia.org/wiki/Silicon_Graphics

https://it.wikipedia.org/wiki/Oracle_Solaris

https://it.wikipedia.org/wiki/Virtual_Address_eXtension

In pratica un barrel processor che gira ad F hertz di clock e con pipeline ad N stadi, COME MINIMO é equivalente ad N cpu che girano ad un clock di F/N Hertz.

Non é come una cpu superscalare con N thread, ma é molto più semplice ed i tempi di esecuzione dei singoli thread non fluttuano in base a quanti thread hardware sono attivi (cosa molto utile ad esempio per simulare in software parte dell'hardware di gestione di una certa interfaccia).

Credo che Risc-V sia il set di istruzioni implementato con più microarchitetture differenti (bit-seriale, von Neuman, Harvard, pipelined, superscalare, multithreaded e barrel processor).

Devi effettuare il login per poter commentare

Se non sei ancora registrato, puoi farlo attraverso questo form.

Se sei già registrato e loggato nel sito, puoi inserire il tuo commento.

Si tenga presente quanto letto nel regolamento, nel rispetto del "quieto vivere".